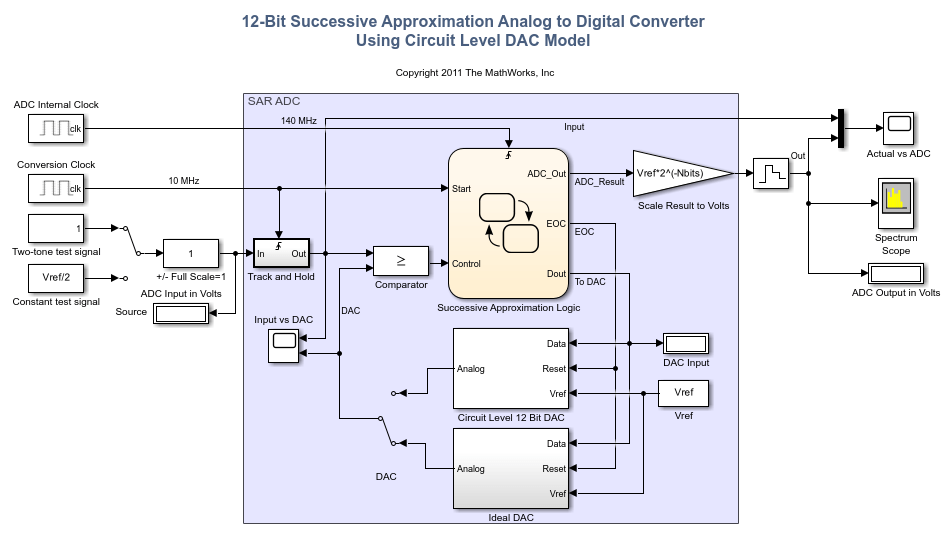

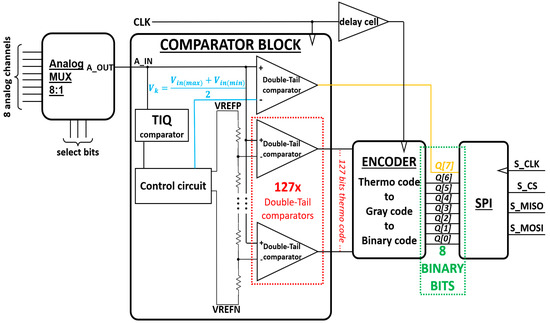

Sensors | Free Full-Text | Design of a Low-Power and Low-Area 8-Bit Flash ADC Using a Double-Tail Comparator on 180 nm CMOS Process

![PDF] A 4.8-bit ENOB 5-bit 500MS/s binary-search ADC with minimized number of comparators | Semantic Scholar PDF] A 4.8-bit ENOB 5-bit 500MS/s binary-search ADC with minimized number of comparators | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/9482935d690541653ea3b71a7a41429ebd4c9113/2-Figure3-1.png)

PDF] A 4.8-bit ENOB 5-bit 500MS/s binary-search ADC with minimized number of comparators | Semantic Scholar

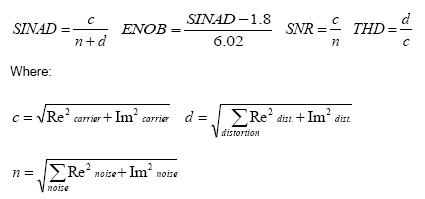

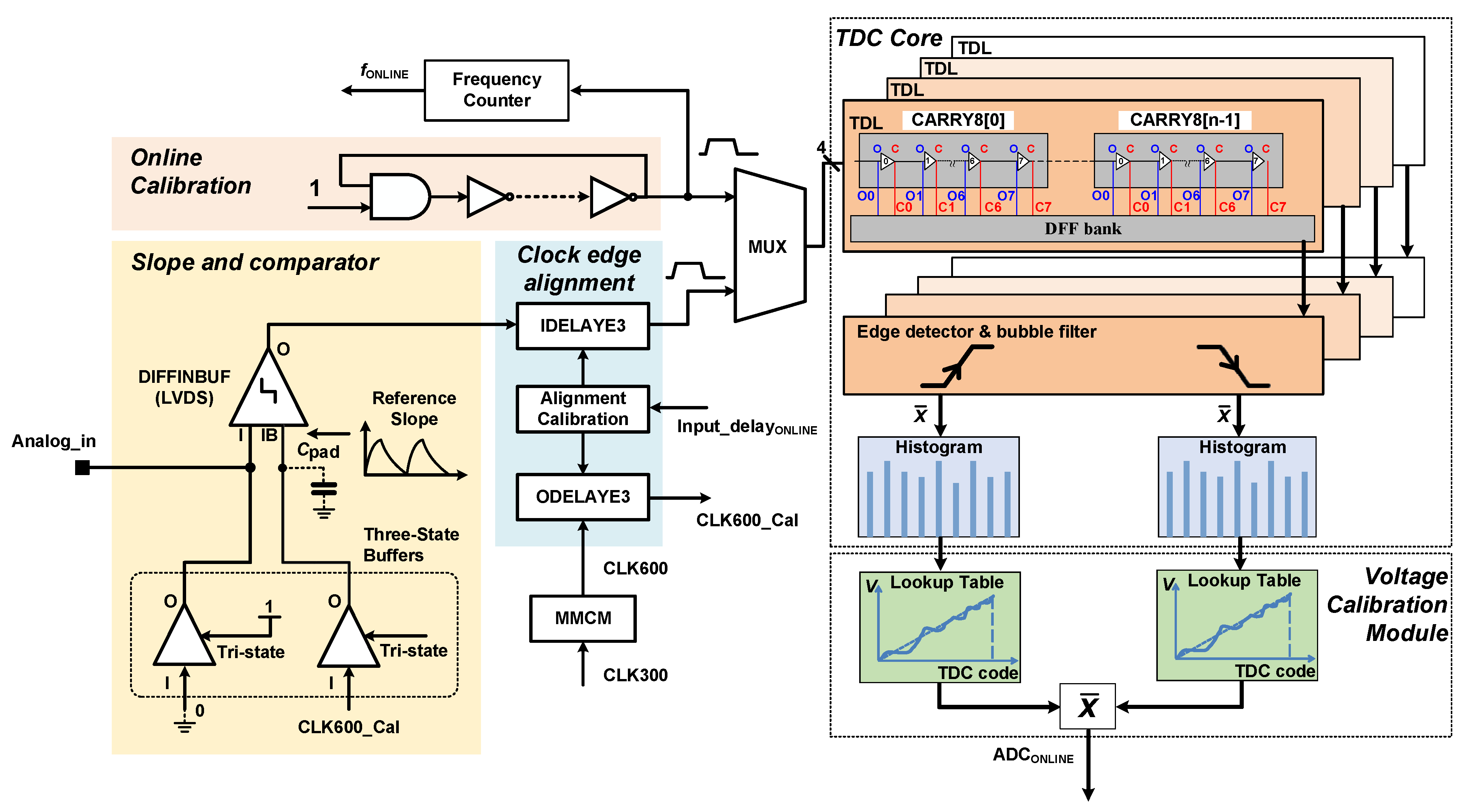

Sensors | Free Full-Text | A 7.4-Bit ENOB 600 MS/s FPGA-Based Online Calibrated Slope ADC without External Components

![PDF] ENOB calculation for ADCs with input-correlated quantization error using a sine-wave test | Semantic Scholar PDF] ENOB calculation for ADCs with input-correlated quantization error using a sine-wave test | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/945e4ece05a5ef6b52c68668cc4afb347c6ebbb6/1-Figure1-1.png)

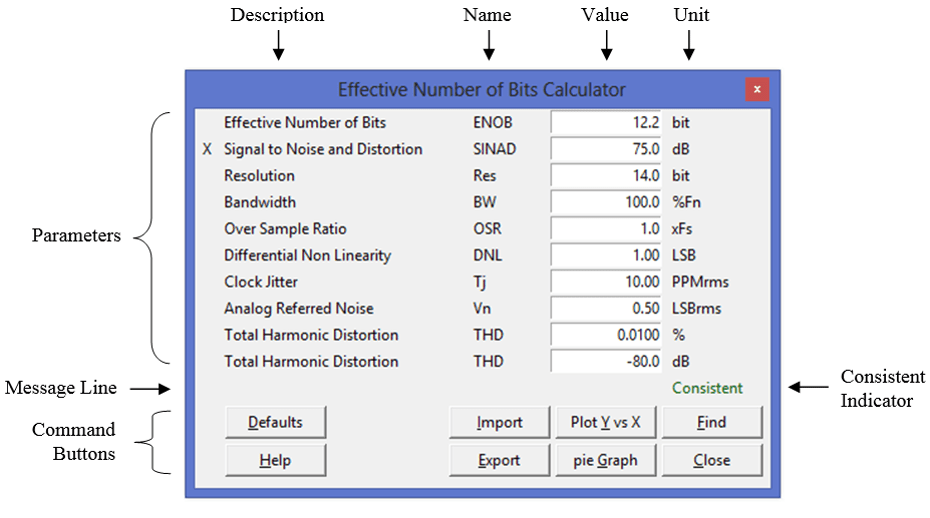

PDF] ENOB calculation for ADCs with input-correlated quantization error using a sine-wave test | Semantic Scholar

ENOB versus number of cycle for standard and modified IC ADC and for 0... | Download Scientific Diagram

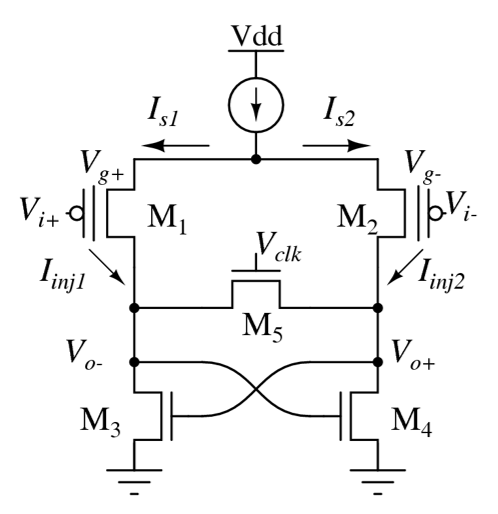

Low‐noise dynamic comparator circuit with selectable input‐referred thermal noise voltage - Yazid - 2018 - Electronics Letters - Wiley Online Library

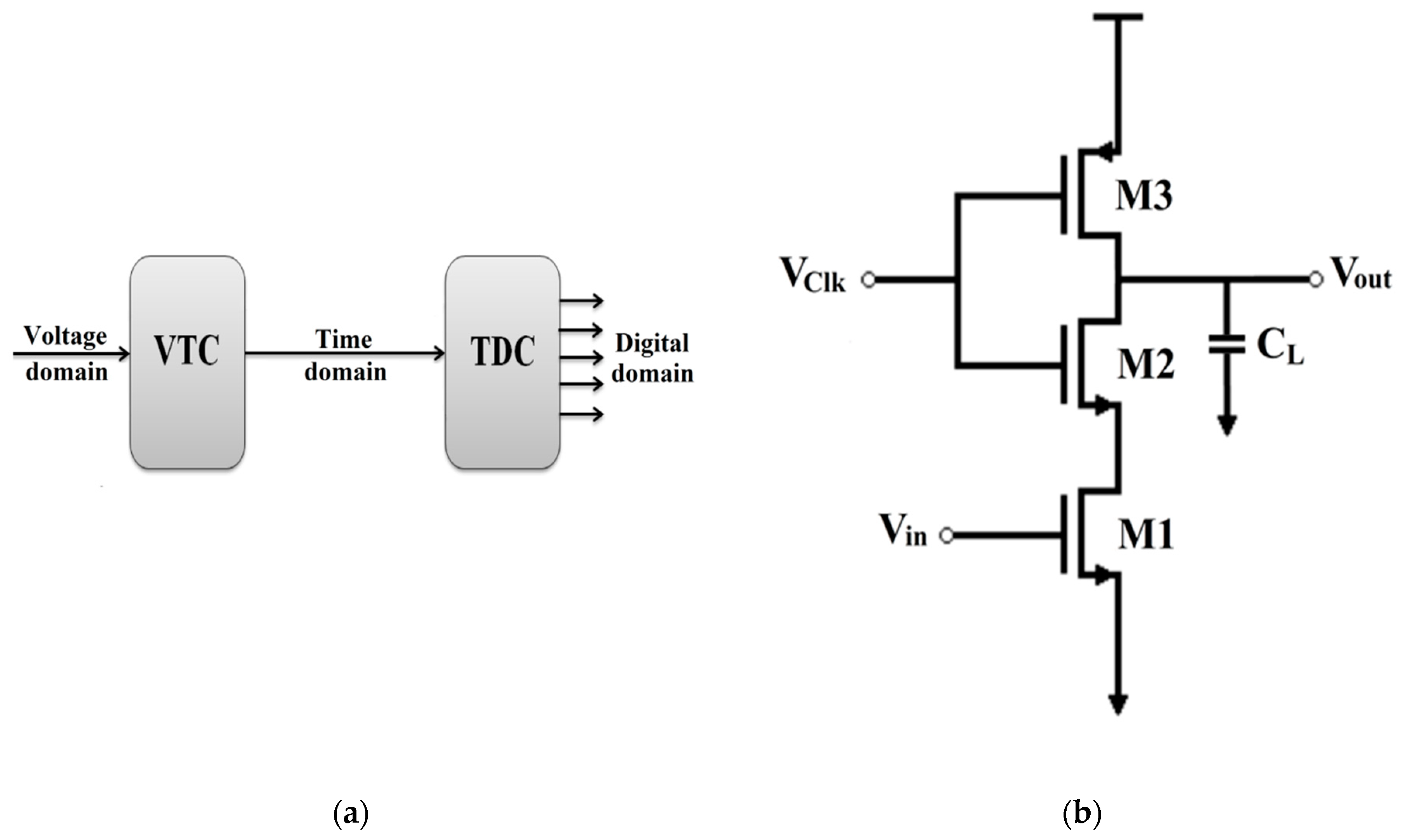

Electronics | Free Full-Text | A Novel Highly Linear Voltage-To-Time Converter (VTC) Circuit for Time-Based Analog-To-Digital Converters (ADC) Using Body Biasing

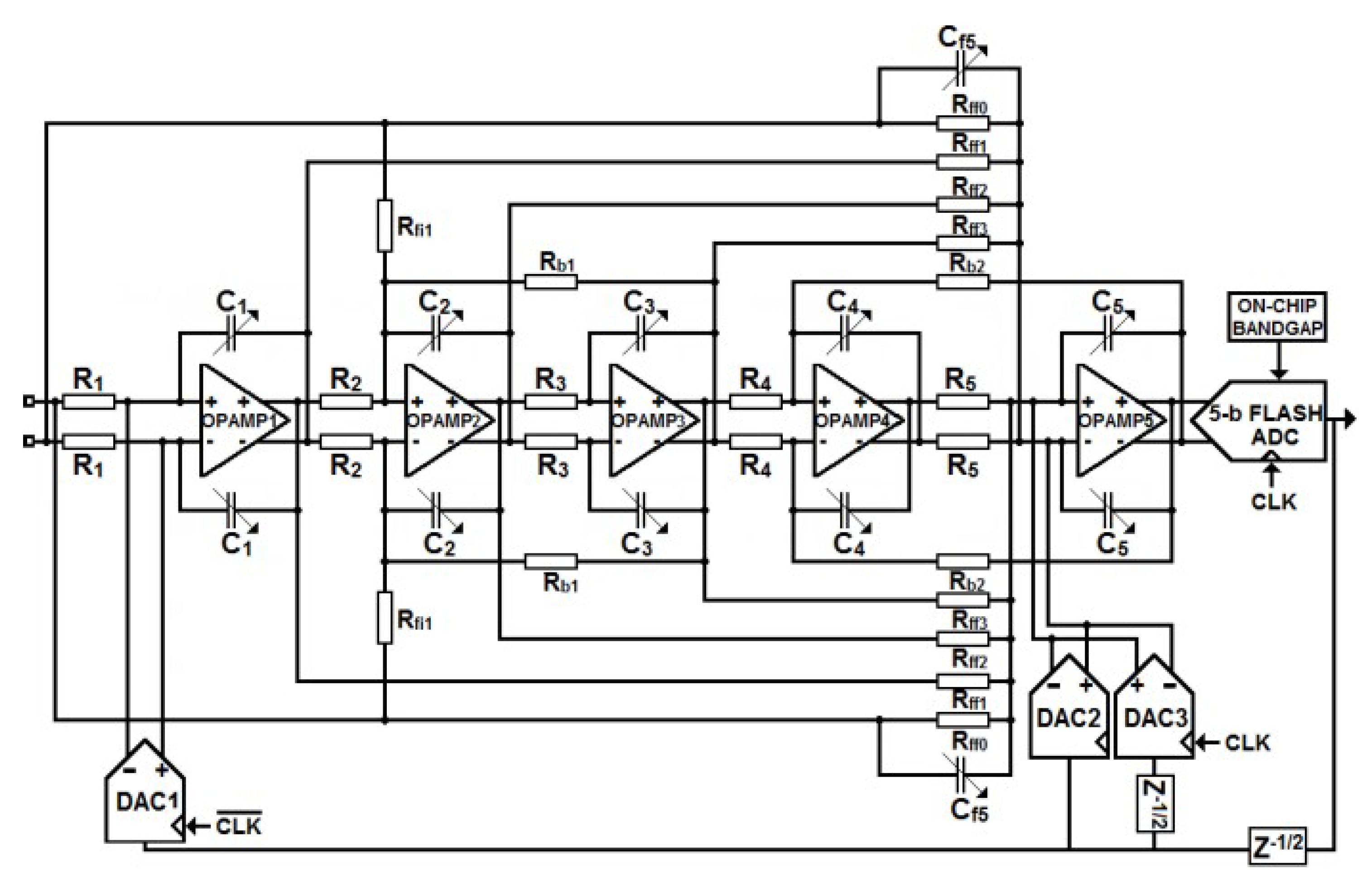

Sensors | Free Full-Text | A 40 MHz 11-Bit ENOB Delta Sigma ADC for Communication and Acquisition Systems

ENOB of IC ADC as a function of number of cycles for different DAC In... | Download Scientific Diagram