PDF) Resonant Tunneling Diode/HBT D-Flip Flop ICs Using Current Mode Logic-Type Monostable-Bistable Transition Logic Element with Complementary Outputs | Taeho Kim - Academia.edu

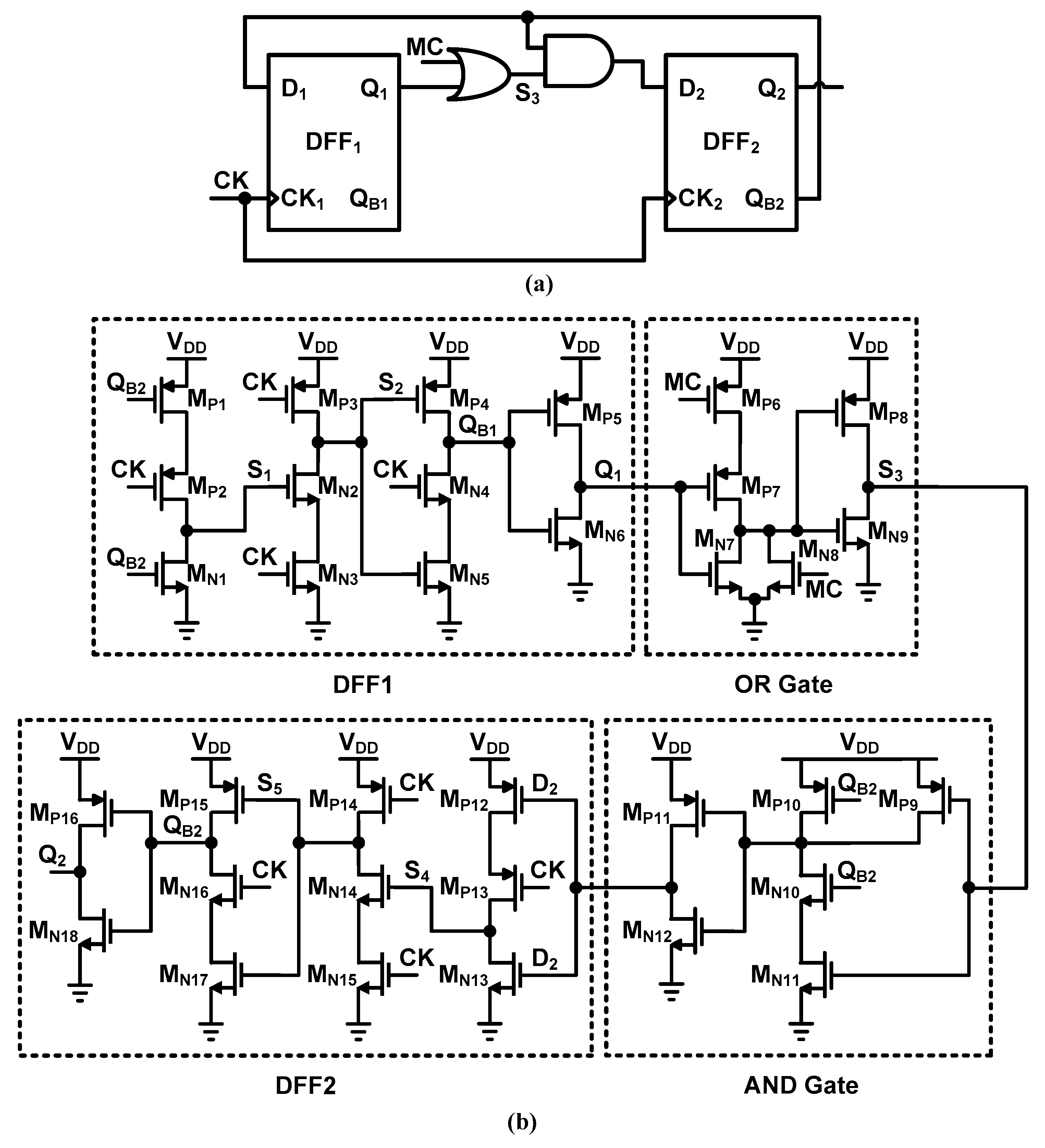

Electronics | Free Full-Text | High-Speed Wide-Range True-Single-Phase-Clock CMOS Dual Modulus Prescaler

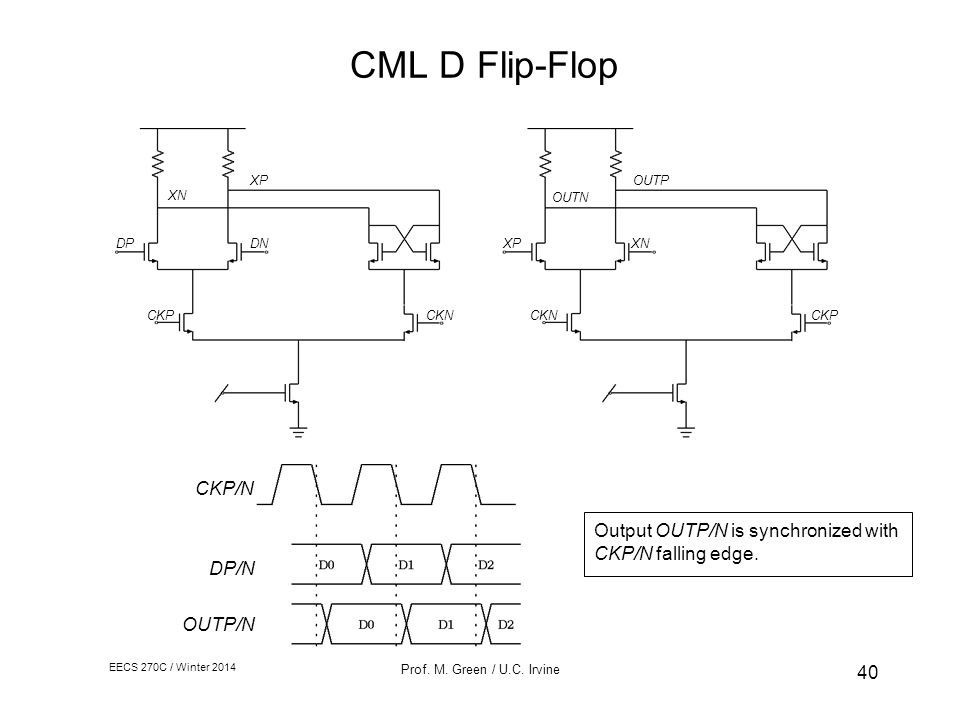

![PDF] High-Frequency CML Clock Dividers in 0.13- (cid:22) m CMOS Operating Up to 38 GHz | Semantic Scholar PDF] High-Frequency CML Clock Dividers in 0.13- (cid:22) m CMOS Operating Up to 38 GHz | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/8e0df65349e98497a606b339d337b44846466658/2-Figure1-1.png)

PDF] High-Frequency CML Clock Dividers in 0.13- (cid:22) m CMOS Operating Up to 38 GHz | Semantic Scholar

An improved current mode logic latch for high‐speed applications - Kumawat - 2020 - International Journal of Communication Systems - Wiley Online Library

Amazon.com: YALFJV Womens Shoes Black Wedges Sandals flip Flops for Women Walking Royal Blue Sandals Nude Sandals for Women Flat White Platform Heels Chunky Women Slides Ladies Strap Sandals Sandals for Women :

An improved current mode logic latch for high‐speed applications - Kumawat - 2020 - International Journal of Communication Systems - Wiley Online Library

Figure 1 from High speed CML latch using active inductor in 0.18μm CMOS technology | Semantic Scholar